四脚有源晶振的典型接法

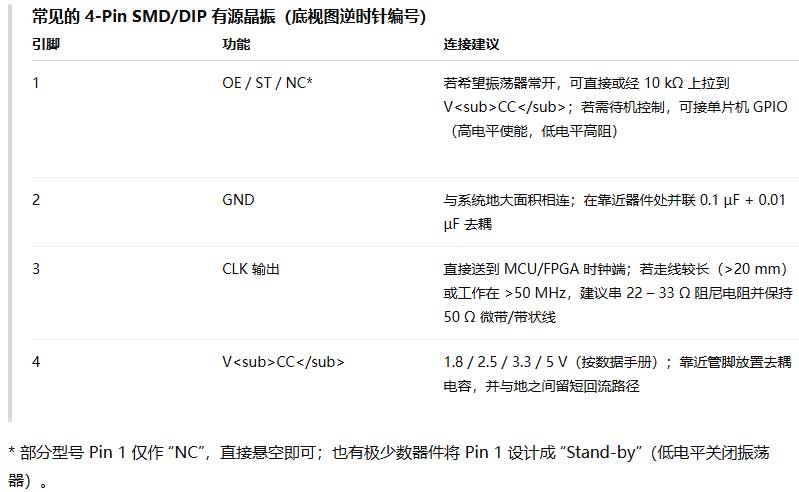

常见的 4-Pin SMD/DIP 有源晶振(底视图逆时针编号)

1| 识别管脚方向

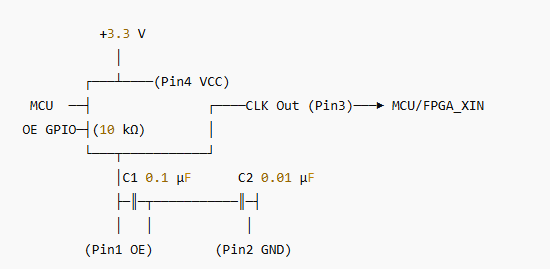

2| 典型原理图连接

关键点

去耦电容紧贴 VCC/GND 两脚;高频时并联两颗不同容量以抑制宽带噪声。

输出走线尽量短直;若板层支持,优先走内层屏蔽或外层带地护墙。

OE 引脚悬空时多为内部上拉(器件始终工作),但仍应阅读数据手册确认。

3 | 不同封装的细微差异

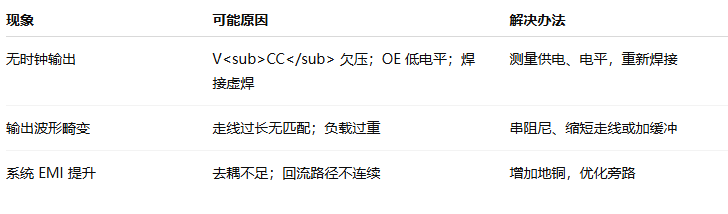

4 | 常见故障与排查

5 | 总结

四脚有源晶振本质上是一颗**“带电源的钟”**:

4 → 电源、2 → 地提供能量;

3 → 输出送时钟;

1 → 开关或悬空决定是否“敲钟”。

只要识别 Pin 1 标记、确保 VCC 稳定、GND 干净、输出线规整,并按需处理 OE,就能让时钟模块稳定工作于

MCU、FPGA 及各种高速数字系统中。